#

# Dual, 4A/2A, 4MHz, Step-Down DC-DC **Regulator with Tracking/Sequencing Capability**

## **General Description**

**Features**

The MAX15021 is a dual-output, pulse-width-modulated (PWM), step-down DC-DC regulator with tracking (coincident and ratiometric) and sequencing options. The device operates from 2.5V to 5.5V and each output can be adjusted from 0.6V to the input supply (VAVIN). The MAX15021 delivers up to 4A (regulator 1) and 2A (regulator 2) of output current. This device offers the ability to adjust the switching frequency from 500kHz to 4MHz and provides the capability of optimizing the design in terms of size and performance.

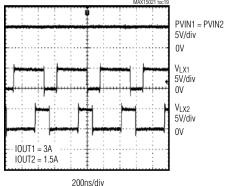

The MAX15021 utilizes a voltage-mode control scheme with external compensation to provide good noise immunity and maximum flexibility in selecting inductor values and capacitor types. The dual switching regulators operate 180° out-of-phase, thereby reducing the RMS input ripple current and thus the size of the input bypass capacitor significantly.

The MAX15021 offers the ability to track (coincident or ratiometric) or sequence during power-up and powerdown operation. When sequencing, it powers up glitchfree into a prebiased output.

Additional features include an internal undervoltage lockout with hysteresis and a digital soft-start/soft-stop for glitch-free power-up and power-down. Protection features include lossless cycle-by-cycle current limit, hiccup-mode output short-circuit protection, and thermal shutdown.

The MAX15021 is available in a space-saving, 5mm x 5mm, 28-pin TQFN-EP package and is specified for operation from -40°C to +125°C temperature range.

**Applications**

**RFID Reader Cards**

Power-over-Ethernet (PoE) IP Phones

Automotive Multimedia

Multivoltage Supplies

Networking/Telecom

## **Ordering Information**

| PART         | TEMP RANGE      | PIN-PACKAGE |

|--------------|-----------------|-------------|

| MAX15021ATI+ | -40°C to +125°C | 28 TQFN-EP* |

|              |                 |             |

+Denotes a lead-free package.

\*EP = Exposed pad.

- ♦ 2.5V to 5.5V Input-Voltage Range

- Dual-Output Synchronous Buck Regulators

- Integrated Switches for 4A and 2A Output Currents

- ♦ 180° Out-Of-Phase Operation

- Output Voltage Adjustable from 0.6V to VAVIN

- Lossless, Cycle-by-Cycle Current Sensing

- External Compensation for Maximum Flexibility

- Digital Soft-Start and Soft-Stop for Tracking **Applications**

- Digital Soft-Start into a Prebiased Load for **Sequencing Applications**

- Sequencing or Coincident/Ratiometric Tracking

- Programmable Switching Frequency from 500kHz to 4MHz

- Thermal Shutdown and Hiccup-Mode Short-**Circuit Protection**

- 20µA Shutdown Current

- 100% Maximum Duty Cycle

- Space-Saving (5mm x 5mm) 28-Pin TQFN Package

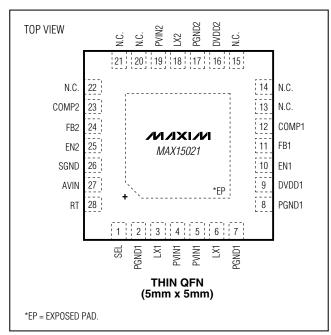

## **Pin Configuration**

## M/X/M

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

AVIN, PVIN\_, DVDD\_, EN\_, FB\_, RT

| , ( , , , , , , , , , , , , , , , , , , |                                    |

|-----------------------------------------|------------------------------------|

| SEL to SGND                             | 0.3V to +6V                        |

| COMP_ to SGND                           | 0.3V to (V <sub>AVIN</sub> + 0.3V) |

| PGND_ to SGND                           | -0.3V to +0.3V                     |

| LX_ Current (Note 1)                    |                                    |

| Regulator 1.                            | 6A                                 |

| Regulator 2                             | 3A                                 |

| Current into Any Pin other than PVIN_,  |                                    |

| LX , and PGND                           | 50mA                               |

Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )

| 28-Pin TQFN (derate 34.5mW/°C above +70°C)2                  | 2758.6mW |

|--------------------------------------------------------------|----------|

| Junction-to-Case Thermal Resistance $(\theta_{JC})$ (Note 2) | 2°C/W    |

| Junction-to-Ambient Thermal Resistance (00 JA)(Note 2        | )29°C/W  |

| Operating Temperature Range40°C                              |          |

| Maximum Junction Temperature                                 | +150°C   |

| Storage Temperature Range60°C                                |          |

| Lead Temperature (soldering, 10s)                            | +300°C   |

Note 1: LX\_ has internal diodes to PGND\_ and PVIN\_. Applications that forward bias these diodes should take care not to exceed the IC's package power dissipation.

**Note 2:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations see <u>www.maxim-ic.com/thermal-tutorial</u>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(V_{AVIN} = V_{PVIN} = V_{DVDD} = 3.3V, V_{PGND} = V_{SGND} = 0V, R_T = 25k\Omega$ , and  $T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 3)

| PARAMETER                            | SYMBOL | CONDITIONS                                                                                            | MIN   | ТҮР   | MAX       | UNITS           |

|--------------------------------------|--------|-------------------------------------------------------------------------------------------------------|-------|-------|-----------|-----------------|

| SYSTEM SPECIFICATIONS                |        | •                                                                                                     |       |       |           |                 |

| Input-Voltage Range                  |        | V <sub>AVIN</sub> = V <sub>PVIN1</sub> = V <sub>PVIN2</sub> = V <sub>DVDD1</sub> = V <sub>DVDD2</sub> | 2.5   |       | 5.5       | V               |

| Undervoltage Lockout Threshold       |        | AVIN rising                                                                                           | 2.1   | 2.2   | 2.3       | V               |

| Undervoltage Lockout Hysteresis      |        |                                                                                                       |       | 0.12  |           | V               |

| Operating Supply Current             |        | $V_{EN}$ = 1.3V, $V_{FB}$ = 0.8V                                                                      |       | 3.5   | 6         | mA              |

| Shutdown Supply Current              |        | $V_{EN_{-}} = 0V$                                                                                     |       | 20    | 65        | μΑ              |

| PWM DIGITAL SOFT-START/SOFT-ST       | OP     |                                                                                                       |       |       |           |                 |

| Soft-Start/Soft-Stop Duration        |        |                                                                                                       |       | 4096  |           | Clock<br>Cycles |

| Reference Voltage Steps              |        |                                                                                                       |       | 64    |           | Steps           |

| PWM ERROR AMPLIFIERS                 |        |                                                                                                       |       |       |           |                 |

| FB1, FB2 Input Bias Current          |        |                                                                                                       | -1    |       | +1        | μΑ              |

| FB1, FB2 Voltage Set-Point           |        |                                                                                                       | 0.593 | 0.599 | 0.605     | V               |

| COMP1, COMP2 Voltage Range           |        | I <sub>COMP</sub> = -250µA to +250µA                                                                  | 0.3   | VA    | VIN - 0.5 | V               |

| Error-Amplifier Open-Loop Gain       |        |                                                                                                       |       | 80    |           | dB              |

| Error-Amplifier Unity-Gain Bandwidth |        |                                                                                                       |       | 12    |           | MHz             |

| POWER MOSFETs                        |        |                                                                                                       |       |       |           |                 |

| Regulator 1 p-Channel MOSFET RDSON   |        | V <sub>DVDD1</sub> = 5V                                                                               |       | 50    | 90        | mΩ              |

| Regulator 1 n-Channel MOSFET RDSON   |        | V <sub>DVDD1</sub> = 5V                                                                               |       | 30    | 50        | mΩ              |

| Regulator 1 Gate Charge              |        | V <sub>DVDD1</sub> = 5V                                                                               |       | 8     |           | nC              |

| Maximum LX1 RMS Current              |        |                                                                                                       |       | 4     |           | А               |

| Regulator 2 p-Channel MOSFET RDSON   |        | V <sub>DVDD2</sub> = 5V                                                                               |       | 100   | 180       | mΩ              |

| Regulator 2 n-Channel MOSFET RDSON   |        | V <sub>DVDD2</sub> = 5V                                                                               |       | 60    | 100       | mΩ              |

| Regulator 2 Gate Charge              |        | V <sub>DVDD2</sub> = 5V                                                                               |       | 4     |           | nC              |

| Maximum LX2 RMS Current              |        |                                                                                                       |       | 2     |           | А               |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVIN} = V_{PVIN} = V_{DVDD} = 3.3V, V_{PGND} = V_{SGND} = 0V, R_T = 25k\Omega$ , and  $T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 3)

| PARAMETER                                                                 | SYMBOL          | CONDITIONS                                                          | MIN                      | ТҮР                  | MAX       | UNITS           |  |

|---------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------|--------------------------|----------------------|-----------|-----------------|--|

| PWM CURRENT LIMIT AND HICCUP                                              | MODE            |                                                                     |                          |                      |           |                 |  |

|                                                                           |                 | V <sub>AVIN</sub> = 3.3V                                            | 4.5                      | 4.9                  | 5.3       | A               |  |

| Regulator 1 Peak Current Limit                                            |                 | $V_{AVIN} = 2.5V$                                                   | 3.4                      | 3.65                 | 3.95      |                 |  |

|                                                                           |                 | $V_{AVIN} = 3.3V$                                                   | 4.0                      | 4.9                  | 5.65      | A               |  |

| Regulator 1 Valley Current Limit                                          |                 | $V_{AVIN} = 2.5V$                                                   | 3.0                      | 3.7                  | 4.25      | A               |  |

| Pagulator 2 Pook Current Limit                                            |                 | $V_{AVIN} = 3.3V$                                                   | 2.25                     | 2.45                 | 2.65      | A               |  |

| Regulator 2 Peak Current Limit                                            |                 | $V_{AVIN} = 2.5V$                                                   | 1.70                     | 1.85                 | 1.98      |                 |  |

| Regulator 2 Valley Current Limit                                          |                 | $V_{AVIN} = 3.3V$                                                   | 2.0                      | 2.5                  | 2.83      | А               |  |

| negulator 2 valley Current Limit                                          |                 | $V_{AVIN} = 2.5V$                                                   | 1.5                      | 1.85                 | 2.13      |                 |  |

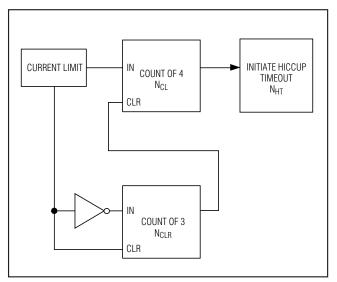

| Number of Cumulative Current-Limit<br>Events to Hiccup                    | N <sub>CL</sub> |                                                                     |                          | 4                    |           | Clock<br>Cycles |  |

| Number of Consecutive Noncurrent<br>Limit Cycles to Clear N <sub>CL</sub> | NCLR            |                                                                     |                          | 3                    |           | Clock<br>Cycles |  |

| Hiccup Timeout                                                            | N <sub>HT</sub> |                                                                     |                          | 8192                 |           | Clock<br>Cycles |  |

| ENABLE/SEL                                                                |                 | •                                                                   |                          |                      |           |                 |  |

| EN_ Threshold                                                             |                 | V <sub>EN</sub> _rising                                             | 1.207                    | 1.225                | 1.243     | V               |  |

| EN_ Hysteresis                                                            |                 |                                                                     |                          | 0.12                 |           | V               |  |

| EN_ Input Current                                                         |                 |                                                                     | -2.5                     |                      | +2.5      | μA              |  |

| SEL High Threshold                                                        |                 |                                                                     | 0.85 x V <sub>AVIN</sub> |                      |           | V               |  |

| SEL Low Threshold                                                         |                 |                                                                     |                          | 0.2                  | 2 x Vavin | V               |  |

| SEL Input Bias Current                                                    |                 | Present only during startup                                         | -100                     |                      | +100      | μA              |  |

| OSCILLATOR                                                                |                 |                                                                     |                          |                      |           |                 |  |

| Switching Frequency Range                                                 | fsw             | f <sub>SW</sub> = 3MHz x [V <sub>RT</sub> (V)/1.067(V)]<br>(Note 4) | 500                      |                      | 4000      | kHz             |  |

|                                                                           |                 | f <sub>SW</sub> ≤ 1500kHz                                           | -6                       |                      | +6        | •               |  |

| Oscillator Accuracy                                                       |                 | f <sub>SW</sub> > 1500kHz                                           | -10                      |                      | +10       | %               |  |

| Phase Shift Between Regulators                                            |                 |                                                                     |                          | 180                  |           | Degrees         |  |

| RT Current                                                                |                 | 0 < V <sub>RT</sub> < 1.067V                                        | 31.30                    | 32                   | 32.58     | μA              |  |

| RT Voltage Range                                                          | V <sub>RT</sub> |                                                                     | 0.13                     |                      | 1.067     | V               |  |

| Minimum Controllable On-Time                                              |                 |                                                                     |                          | 60                   |           | ns              |  |

| Minimum Controllable Off-Time                                             |                 |                                                                     |                          | 60                   |           | ns              |  |

| PWM Ramp Amplitude                                                        |                 |                                                                     |                          | V <sub>AVIN</sub> /4 |           | V               |  |

| PWM Ramp Valley                                                           |                 |                                                                     |                          | 0.3                  |           | V               |  |

| THERMAL SHUTDOWN                                                          |                 |                                                                     | ·                        |                      |           |                 |  |

| Thermal Shutdown Temperature                                              |                 | Temperature rising                                                  |                          | +160                 |           | °C              |  |

| Thermal Shutdown Hysteresis                                               |                 |                                                                     |                          | 15                   |           | °C              |  |

**Note 3:** Specifications are 100% production tested at  $T_A = +25^{\circ}C$  and  $T_A = +125^{\circ}C$ . Maximum and minimum specifications over temperature are guaranteed by design.

Note 4: When operating with AVIN = 2.5V, the maximum switching frequency should be derated to 3MHz.

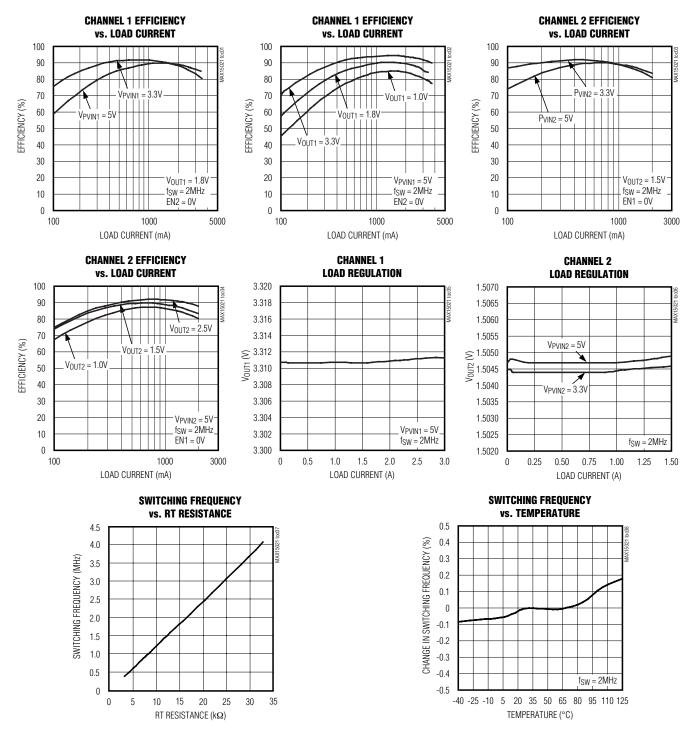

$(V_{AVIN} = V_{DVDD1} = V_{DVDD2} = V_{PVIN1} = V_{PVIN2} = 5V, V_{OUT1} = 3.3V, V_{OUT2} = 1.5V, V_{PGND_} = 0V, R_T = 16.5k\Omega$ . T<sub>A</sub> = +25°C, unless otherwise noted.)

**Typical Operating Characteristics**

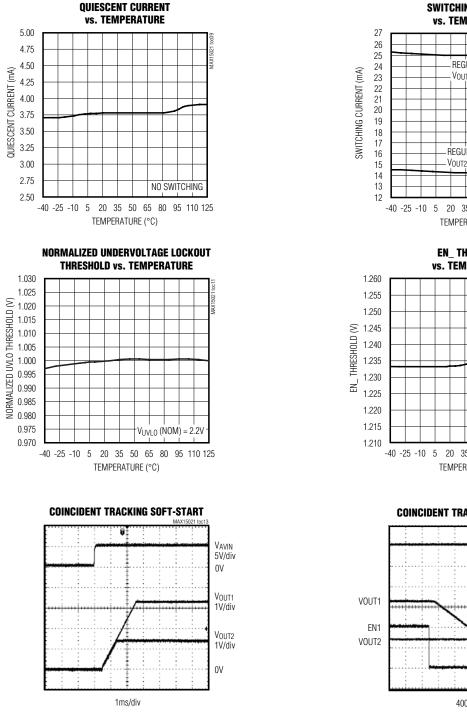

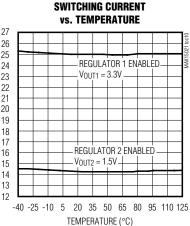

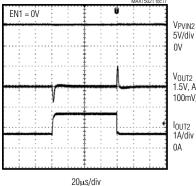

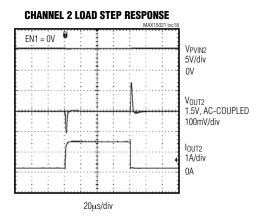

## **Typical Operating Characteristics (continued)**

(VAVIN = VDVDD1 = VDVDD2 = VPVIN1 = VPVIN2 = 5V, VOUT1 = 3.3V, VOUT2 = 1.5V, VPGND\_ = 0V, RT = 16.5kΩ. TA = +25°C, unless otherwise noted.)

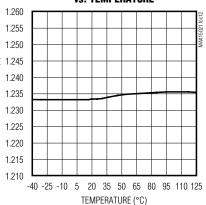

**EN\_ THRESHOLD** vs. TEMPERATURE

MAX15021

M /X / M

## **Typical Operating Characteristics (continued)**

$(V_{AVIN} = V_{DVDD1} = V_{DVDD2} = V_{PVIN1} = V_{PVIN2} = 5V, V_{OUT1} = 3.3V, V_{OUT2} = 1.5V, V_{PGND_} = 0V, R_T = 16.5k\Omega$ . T<sub>A</sub> = +25°C, unless otherwise noted.)

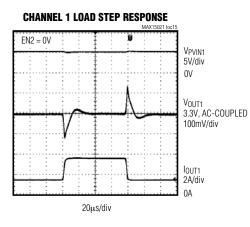

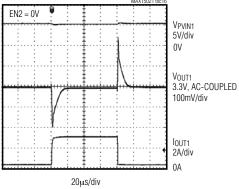

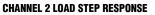

## CHANNEL 1 LOAD STEP RESPONSE

V<sub>OUT2</sub> 1.5V, AC-COUPLED 100mV/div

## **Pin Description**

| PIN                       | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                     |  |

|---------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                         | SEL   | Track/Sequence Select Input. Connect SEL to ground to configure the device as a sequencer. Conn SEL to AVIN for tracking with output 1 as the master. Leave SEL unconnected for tracking with output as the master. Use the output with the higher voltage as the master and the output with the lower voltage as the slave. |  |

| 2, 7, 8                   | PGND1 | Power Ground Connection for Regulator 1. Connect the negative terminals of the input and output filter capacitor to PGND1. Connect PGND1 externally to SGND at a single point, typically at the negative terminal of the input capacitor.                                                                                    |  |

| 3, 6                      | LX1   | Inductor Connection for Regulator 1. LX1 is the drain connection of the internal high-side p-channel MOSFET and the drain connection of the internal synchronous n-channel MOSFET for regulator 1.                                                                                                                           |  |

| 4, 5                      | PVIN1 | Input Supply Voltage for Regulator 1. Connect to an external voltage source from 2.5V to 5.5V. Bypass PVIN1 to PGND1 with a $1\mu$ F (min) ceramic capacitor.                                                                                                                                                                |  |

| 9                         | DVDD1 | Switch Driver Supply for Regulator 1. Connect externally to PVIN1.                                                                                                                                                                                                                                                           |  |

| 10                        | EN1   | Enable Input for Regulator 1. When configured as a sequencer, EN1 must exceed 1.225V (typ) for the PWM controller to begin regulating output 1. When configured as a tracker, connect EN1 to the center tap of a resistive divider from the regulator 2 output.                                                              |  |

| 11                        | FB1   | Feedback Regulation Point for Regulator 1. Connect FB1 to the center tap of a resistive divider from the regulator 1 output to SGND to set the output voltage. The FB1 voltage regulates to 0.6V (typ).                                                                                                                      |  |

| 12                        | COMP1 | Error-Amplifier Output for Regulator 1. Connect COMP1 to the compensation feedback network.                                                                                                                                                                                                                                  |  |

| 13, 14, 15,<br>20, 21, 22 | N.C.  | No Connection. Do not connect.                                                                                                                                                                                                                                                                                               |  |

| 16                        | DVDD2 | Switch Driver Supply for Regulator 2. Connect externally to PVIN2.                                                                                                                                                                                                                                                           |  |

| 17                        | PGND2 | Power Ground Connection for Regulator 2. Connect the negative terminals of the input and output f capacitors to PGND2. Connect PGND2 externally to SGND at a single point, typically at the negative terminal of the input capacitor.                                                                                        |  |

| 18                        | LX2   | Inductor Connection for Regulator 2. LX2 is the drain connection of the internal high-side p-channel MOSFET and the drain connection of the internal synchronous n-channel MOSFET for regulator 2.                                                                                                                           |  |

| 19                        | PVIN2 | Input Supply Voltage for Regulator 2. Connect to an external voltage source from 2.5V to 5.5V. Bypass PVIN2 to PGND2 with a $1\mu$ F (min) ceramic capacitor.                                                                                                                                                                |  |

| 23                        | COMP2 | Error-Amplifier Output for Regulator 2. Connect COMP2 to the compensation feedback network.                                                                                                                                                                                                                                  |  |

| 24                        | FB2   | Feedback Regulation Point for Regulator 2. Connect to the center tap of a resistive divider from the regulator 2 output to SGND to set the output voltage. The FB2 voltage regulates to 0.6V (typ).                                                                                                                          |  |

| 25                        | EN2   | Enable Input for Regulator 2. When configured as a sequencer, EN2 must exceed 1.225V (typ) for the PWM controller to begin regulating output 1. When configured as a tracker, connect EN1 to the center tap of a resistive divider from the regulator 1 output.                                                              |  |

| 26                        | SGND  | Signal Ground. Connect SGND to PGND_ at a single point, typically near negative terminal of the input bypass capacitor.                                                                                                                                                                                                      |  |

| 27                        | AVIN  | Input Voltage. Bypass AVIN to SGND with a 100nF (min) ceramic capacitor.                                                                                                                                                                                                                                                     |  |

| 28                        | RT    | Oscillator Timing Resistor Connection. Connect a $4.2k\Omega$ to $33k\Omega$ resistor from RT to SGND to program the switching frequency from 500kHz to 4MHz.                                                                                                                                                                |  |

| _                         | EP    | Exposed Pad. Connect EP to a large copper plane at SGND potential to improve thermal dissipation. Do not use as the main SGND connection.                                                                                                                                                                                    |  |

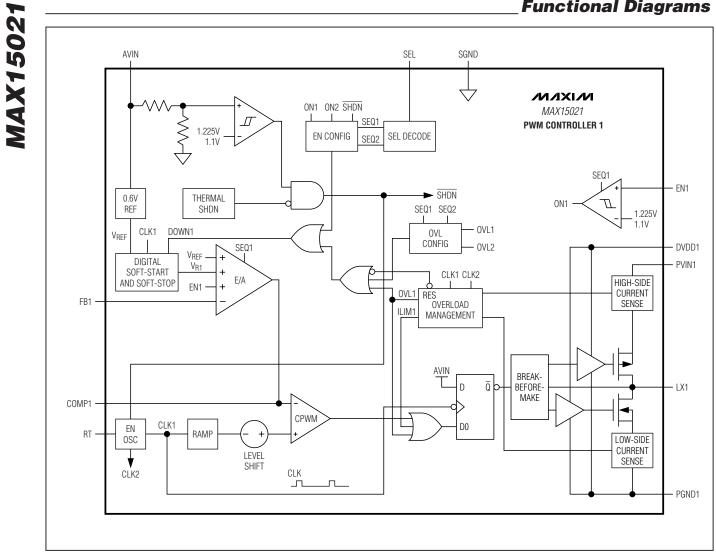

**Functional Diagrams**

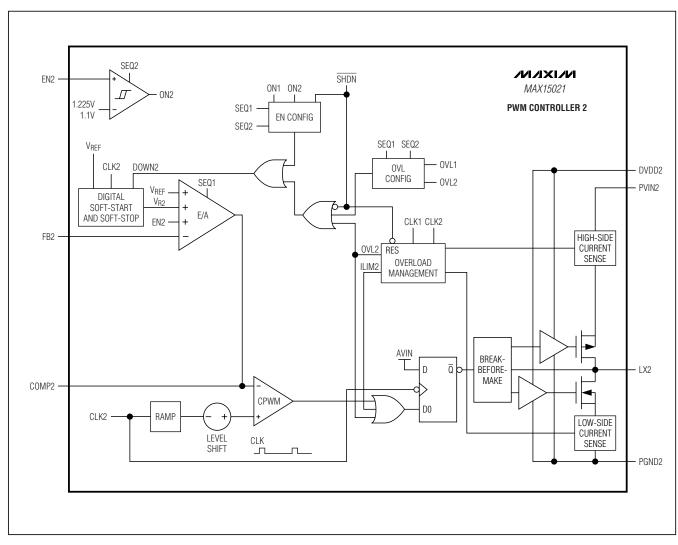

## \_Functional Diagrams (continued)

**MAX15021**

## **Detailed Description**

The MAX15021 incorporates dual-output, PWM, stepdown, DC-DC regulators with tracking and sequencing options. The device operates over the input-voltage range of 2.5V to 5.5V. Each PWM regulator provides an adjustable output down to 0.6V and delivers up to 4A (regulator 1) and 2A (regulator 2) of load current. The high switching frequency (up to 4MHz) and integrated power switches optimize the MAX15021 for high-performance and small-size power management solutions.

Each of the MAX15021 PWM regulator sections utilizes a voltage-mode control scheme for good noise immunity and offers external compensation allowing for maximum flexibility with a wide selection of inductor values and capacitor types. The device operates at a fixed switching frequency that is programmable from 500kHz to 4MHz with a single resistor. Operating the regulators with 180° out-of-phase clocking, and at frequencies up to 4MHz, significantly reduces the RMS input ripple current. The resulting peak input current reduction (and increase in the ripple frequency) significantly reduces the required amount of input bypass capacitance.

The MAX15021 provides coincident tracking, ratiometric tracking, or sequencing to allow tailoring of powerup/power-down sequence depending on the system requirements. When sequencing, it powers up glitchfree into a prebiased output.

The MAX15021 includes internal undervoltage lockout with hysteresis, digital soft-start/soft-stop for "glitch-free" power-up and power-down. Protection features include lossless, cycle-by-cycle current limit, hiccup-mode output short-circuit protection, and thermal shutdown.

## Undervoltage Lockout (UVLO)

The supply voltage (VAVIN) must exceed the default UVLO threshold before any operation starts. The UVLO circuitry keeps the MOSFET drivers, oscillator, and all the internal circuitry shut down to reduce current consumption. The UVLO rising threshold is 2.2V (typ) with a 120mV (typ) hysteresis.

#### **Digital Soft-Start/Soft-Stop**

The MAX15021 soft-start feature allows the load voltage to ramp up in a controlled manner, eliminating output-voltage overshoot. Soft-start begins after VAVIN exceeds the undervoltage lockout threshold and the enable input is above 1.7V (typ). The soft-start circuitry ramps up the reference voltage, controlling the rate of rise of the output voltage, and reducing input surge currents during startup. The soft-start duration is 4096 clock cycles. The output voltage is incremented through 64 equal steps. The output reaches regulation when soft-start is completed, regardless of the output capacitance and load.

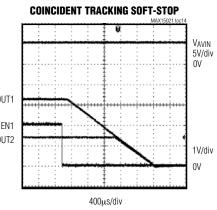

For tracking applications, soft-stop commences when the enable input falls below 1.1V (typ). The soft-stop circuitry ramps down the reference voltage controlling the output-voltage rate of fall. The output voltage is decremented through 64 equal steps in 4096 clock cycles.

#### Oscillator

Use an external resistor at RT to program the MAX15021 switching frequency from 500kHz to 3MHz. Calculate the appropriate resistor at RT for the desired output switching frequency ( $f_{SW}$ ):

$$\mathsf{R}_{\mathsf{T}}[\mathsf{k}\Omega] = \frac{\mathsf{f}_{\mathsf{SW}}[\mathsf{k}\mathsf{H}z] \times 1.067[\mathsf{V}]}{32[\mu\mathsf{A}] \times 4[\mathsf{M}\mathsf{H}z]}$$

#### **Tracking/Sequencing**

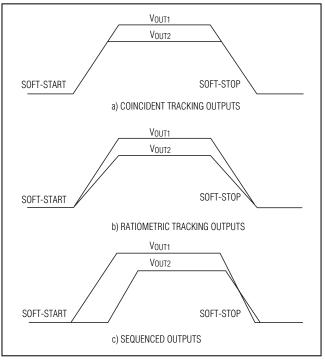

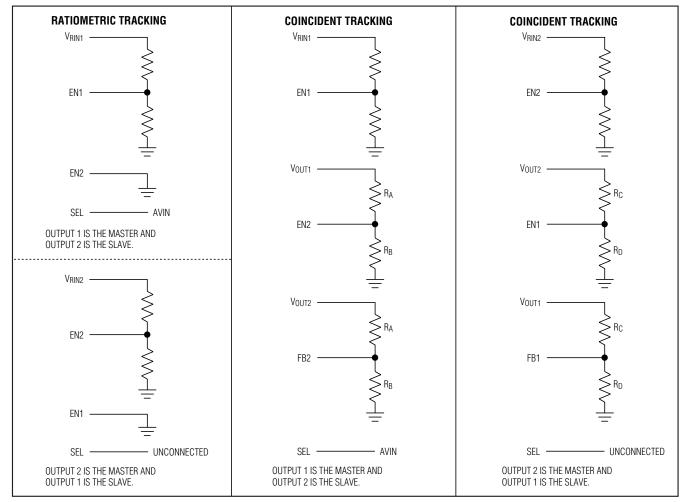

The MAX15021 features coincident/ratiometric tracking and sequencing (see Figure 1). Connect SEL to ground to configure the device as sequencer. Connect SEL to AVIN for tracking with output 1 as the master. Leave SEL unconnected for tracking with output 2 as the master. Assign the output with the higher voltage as the master.

Figure 1. Graphical Representation of Coincident Tracking, Ratiometric Tracking, and Sequencing

#### Coincident/Ratiometric Tracking

The enable inputs in conjunction with digital soft-start and soft-stop provide coincident/ratiometric tracking. Track an output voltage by connecting a resistive divider from the output being tracked to its enable input. For example, for V<sub>OUT2</sub> to coincidentally track V<sub>OUT1</sub>, connect the same resistive divider used for FB2, from V<sub>OUT1</sub> to EN2 to SGND (see Figure 2).

Track ratiometrically by connecting EN\_ to SGND. This synchonizes the soft-start and soft-stop of all the regulator references, and hence their respective output voltages will track ratiometrically (see Figure 2).

When the MAX15021 regulators are configured as voltage trackers, output short-circuit fault conditions at either master or slave output are handled carefully—neither the master nor slave output will remain energized when the other output is shorted to ground. When the slave is shorted and enters hiccup mode, the master will soft-stop. When the master is shorted and the part enters in hiccup mode, the slave will ratiometrically softstop. Coming out of hiccup mode, both outputs will softstart coincidently or ratiometrically depending on their initial configuration. During the thermal shutdown or power-off when the input falls below its UVLO, the output voltages decrease at a rate depending on the respective output capacitance and load.

See Figure 1 for a graphical representation of coincident/ratiometric tracking.

#### Sequencing

When sequencing, the voltage at the enable inputs must exceed 1.225V (typ) for each PWM controller to start (see Figure 1c).

Figure 2. Ratiometric Tracking and Coincident Tracking Configurations

#### Error Amplifier

The output of the internal voltage-mode error amplifier (COMP\_) is provided for frequency compensation (see the *Compensation-Design Guidelines* section). FB\_ is the inverting input of the error amplifier. The error amplifier has an 80dB open-loop gain and a 12MHz gain bandwidth (GBW) product.

#### Output Short-Circuit Protection (Hiccup Mode)

The MAX15021 features lossless, high-side peak current limit and low-side, valley current limit. At short duty cycles, both limits are active. At high duty cycles, only the high-side peak current limit is active. Either limit causes the hiccup mode count ( $N_{CL}$ ) to increment.

For duty cycles less than 50%, the low-side valley current limit is active. Once the high-side MOSFET turns off, the voltage across the low-side MOSFET is monitored. If this voltage does not exceed the current-limit threshold at the end of the cycle, the high-side MOSFET turns on normally at the start of the next cycle. If the voltage exceeds the current-limit threshold just before the beginning of a new PWM cycle, the controller skips that cycle. During severe overload or short-circuit conditions, the switching frequency of the device appears to decrease because the on-time of the low-side MOSFET extends beyond a clock cycle.

If the current-limit threshold is exceeded for more than four cumulative clock cycles (N<sub>CL</sub>), the device shuts down for 8192 clock cycles (hiccup timeout) and then restarts with a soft-start sequence. If three consecutive cycles pass without a current-limit event, the count of N<sub>CL</sub> is cleared (see Figure 3). Hiccup mode protects the device against a continuous output short circuit.

The internal current limit is constant from 5.5V down to 3V and decreases linearly by 50% from 3V to 2V. See the *Electrical Characteristics* table.

#### **Thermal-Overload Protection**

The MAX15021 features an integrated thermal-overload protection with temperature hysteresis. Thermal-overload protection limits the total power dissipation in the device and protects it in the event of an extended thermal fault condition. When the die temperature exceeds +160°C, an internal thermal sensor shuts down the device, turning off the internal power MOSFETs and allowing the die to cool. After the die temperature falls by +15°C, the part restarts with a soft-start sequence.

Figure 3. Hiccup-Mode Block Diagram

#### Startup into a Prebiased Output (Sequencing Mode)

In sequencing mode, the regulators start into a prebiased output and soft-stop is disabled. During soft-start, the complementary switching sequence is inhibited until the PWM comparator commands its first PWM pulse. Until then, the converters do not sink current from the outputs. The first PWM pulse occurs when the ramping reference voltage increases above the FB\_ voltage.

## **PWM Controllers** Design Procedure

#### **Setting the Switching Frequency**

Connect a  $4.2k\Omega$  to  $33k\Omega$  resistor from RT to SGND to program the switching frequency from 500kHz to 4MHz. Calculate the resistor connected to RT using the following equation:

$$R_{T}[k\Omega] = \frac{f_{SW}[kHz] \times 1.067[V]}{32[\mu A] \times 4[MHz]}$$

Higher frequencies allow designs with lower inductor values and less output capacitance. At higher switching frequencies core losses, gate-charge currents, and switching losses increase. When operating from  $V_{AVIN} \leq 3V$ , the switching frequency (fsw) should be derated to 3MHz (maximum).

#### **Effective Input-Voltage Range**

Although the MAX15021's regulators can operate from input supplies ranging from 2.5V to 5.5V, the input-voltage range can be effectively limited by the MAX15021's duty-cycle limitations for a given output voltage (V<sub>OUT</sub>). The maximum input voltage (V<sub>PVIN\_MAX</sub>) can be effectively limited by the controllable minimum on-time (t<sub>ON(MIN)</sub>):

$$V_{PVIN_MAX}[V] \le \frac{V_{OUT_}[V]}{t_{ON(MIN)}[\mu s] \times f_{SW}[MHz]}$$

where ton(MIN) is 0.06µs (typ).

The minimum input voltage (VPVIN\_MIN) can be effectively limited by the maximum controllable duty cycle and is calculated using the following equation:

$$V_{\text{PVIN}_{\text{MIN}}}[V] \ge \frac{V_{\text{OUT}_{\text{V}}}[V]}{1 - (t_{\text{OFF}(\text{MIN})}[\mu s] \times f_{\text{SW}}[\text{MHz}])}$$

where  $V_{OUT\_}$  is the regulator output voltage and toFF(MIN) is the 0.06  $\mu s$  (typ) controllable off-time.

#### **Inductor Selection**

Three key inductor parameters must be specified for operation with the MAX15021: inductance value (L), peak inductor current (IPEAK), and inductor saturation current (ISAT). The minimum required inductance is a function of operating frequency, input-to-output voltage differential, and the peak-to-peak inductor current  $(\Delta I_{P-P})$ . Higher  $\Delta I_{P-P}$  allows for a lower inductor value. A lower inductance minimizes size and cost and improves large-signal and transient response. However, efficiency is reduced due to higher peak currents and higher peak-to-peak output-voltage ripple for the same output capacitor. A higher inductance increases efficiency by reducing the ripple current; however, resistive losses due to extra wire turns can exceed the benefit gained from lower ripple current levels especially when the inductance is increased without also allowing for larger inductor dimensions. Choose the inductor's peak-to-peak current,  $\Delta I_{P-P}$  in the range of 20% to 50% of the full load current; as a rule of thumb 30% is typical.

Calculate the inductance, L, using the following equation:

$$L[\mu H] = \frac{V_{OUT}[V] \times (V_{PVIN}[V] - V_{OUT}[V])}{V_{PVIN}[V] \times f_{SW}[MHz] \times \Delta I_{P-P}[A]}$$

where  $V_{PVIN}$  is the input supply voltage,  $V_{OUT}$  is the regulator output voltage, and f<sub>SW</sub> is the switching frequency. Use typical values for  $V_{PVIN}$  and  $V_{OUT}$  so that efficiency is optimum for typical conditions. The switching frequency (f<sub>SW</sub>) is programmable between 500kHz and 4MHz (see the *Oscillator* section).

The peak-to-peak inductor current ( $\Delta$ IP-P), which reflects the peak-to-peak output ripple, is largest at the maximum input voltage. See the *Output-Capacitor Selection* section to verify that the worst-case output current ripple is acceptable.

Select an inductor with a saturation current, I<sub>SAT</sub>, higher than the maximum peak current to avoid runaway current during continuous output short-circuit conditions. Also, confirm that the inductor's thermal performances and projected temperature rise above ambient does not exceed its thermal capacity. Many inductor manufacturers provide bias/load current versus temperature rise performance curves (or similar) to obtain this information.

#### **Input-Capacitor Selection**

The discontinuous input current of the buck converter causes large input ripple currents and therefore, the input capacitor must be carefully chosen to withstand the input ripple current and keep the input-voltage ripple within design requirements.

The input-voltage ripple is comprised of  $\Delta V_Q$  (caused by the capacitor discharge) and  $\Delta V_{ESR}$  (caused by the ESR of the input capacitor). The total voltage ripple is the sum of  $\Delta V_Q$  and  $\Delta V_{ESR}$  which peaks at the end of the on-cycle. Calculate the required input capacitance and ESR for a specified ripple using the following equations:

$$\begin{split} \text{ESR}[m\Omega] &= \frac{\Delta \text{V}_{\text{ESR}}[mV]}{\left(I_{\text{LOAD}}(\text{MAX}) + \frac{\Delta I_{\text{P}-\text{P}}}{2}\right)[\text{A}]} \\ \text{C}_{\text{PVIN}}[\mu\text{F}] &= \frac{I_{\text{LOAD}}(\text{MAX})[\text{A}] \times \left(\frac{\text{V}_{\text{OUT}}[V]}{\text{V}_{\text{PVIN}}[V]}\right)}{\Delta \text{V}_{\text{Q}}[V] \times f_{\text{SW}}[\text{MHz}]} \\ \text{\Delta}I_{\text{P}-\text{P}}[\text{A}] &= \frac{\left(\text{V}_{\text{PVIN}} - \text{V}_{\text{OUT}}\right)[V] \times \text{V}_{\text{OUT}}[V]}{\text{V}_{\text{PVIN}}[V] \times f_{\text{SW}}[\text{MHz}] \times L[\mu\text{H}]} \end{split}$$

$I_{LOAD(MAX)}$  is the maximum output current,  $\Delta I_{P-P}$  is the peak-to-peak inductor current, and  $V_{PVIN}$  is the input supply voltage,  $V_{OUT}$  is the regulator output voltage, and fsw is the switching frequency.

Use the following equation to calculate the input ripple when only one regulator is enabled:

$I_{CIN(RMS)}[A] = I_{LOAD(MAX)}[A] \times$

$$\frac{\sqrt{V_{OUT}[V] \times (V_{PVIN} - V_{OUT})[V]}}{V_{PVIN}[V]}$$

The MAX15021 includes UVLO hysteresis to avoid possible unintentional chattering during turn-on. Use additional bulk capacitance if the input source impedance is high. If using a lower input voltage, additional input capacitance helps to avoid possible undershoot below the undervoltage lockout threshold during transient loading.

#### **Output-Capacitor Selection**

The allowed output-voltage ripple and the maximum deviation of the output voltage during load steps determine the required output capacitance and its ESR. The output ripple is mainly composed of  $\Delta V_Q$  (caused by the capacitor discharge) and  $\Delta V_{ESR}$  (caused by the voltage drop across the equivalent series resistance of the output capacitance and its ESR are:

$C_{OUT}[\mu F] = \frac{\Delta I_{P-P}[A]}{8 \times \Delta V_Q[V] \times f_{SW}[MHz]}$  $ESR[m\Omega] = \frac{2 \times \Delta V_{ESR}[mV]}{\Delta I_{P-P}[A]}$

where  $\Delta I_{P-P}$  is the peak-to-peak inductor current, and f<sub>SW</sub> is the switching frequency.

$\Delta V_{ESR}$  and  $\Delta V_Q$  are not directly additive since they are out of phase from each other. If using ceramic capacitors, which generally have low ESR,  $\Delta V_Q$  dominates. If using electrolytic capacitors,  $\Delta V_{ESR}$  dominates.

The allowable deviation of the output voltage during fast load transients also affects the output capacitance. its ESR, and its equivalent series inductance (ESL). The output capacitor supplies the load current during a load step until the controller responds with an increased duty cycle. The response time (tRESPONSE) depends on the gain bandwidth of the controller (see the Compensation-Design Guidelines section). The resistive drop across the output capacitor's ESR  $(\Delta V_{\text{ESR}})$ , the drop across the capacitor's ESL ( $\Delta V_{\text{ESL}}$ ), and the capacitor discharge ( $\Delta V_Q$ ) cause a voltage droop during the load-step (ISTEP). Use a combination of low-ESR tantalum/aluminum electrolyte and ceramic capacitors for better load transient and voltage ripple performance. Nonleaded capacitors and capacitors in parallel help reduce the ESL. Keep the maximum output voltage deviation below the tolerable limits of the electronics being powered.

Use the following equations to calculate the required output capacitance, ESR, and ESL for minimal output deviation during a load step:

$$\begin{split} & \text{ESR}[m\Omega] = \frac{\Delta V_{\text{ESR}}[mV]}{I_{\text{STEP}}[A]} \\ & \text{C}_{\text{OUT}}[\mu\text{F}] = \frac{I_{\text{STEP}}[A] \times t_{\text{RESPONSE}}[\mu\text{S}]}{\Delta V_Q}[V] \\ & \text{ESL[nH]} = \frac{\Delta V_{\text{ESL}}[mV] \times t_{\text{STEP}}[\mu\text{S}]}{I_{\text{STEP}}[A]} \end{split}$$

where  $\mathsf{I}_{\mathsf{STEP}}$  is the load step,  $\mathsf{t}_{\mathsf{STEP}}$  is the rise time of the load step, and  $\mathsf{t}_{\mathsf{RESPONSE}}$  is the response time of the controller.

#### **Compensation-Design Guidelines**

The MAX15021 uses a fixed-frequency, voltage-mode control scheme that regulates the output voltage by comparing the output voltage against a fixed reference. The subsequent "error" voltage that appears at the error-amplifier output (COMP\_) is compared against an internal ramp voltage to generate the required duty cycle of the pulse-width modulator. A second-order lowpass LC filter removes the switching harmonics and passes the DC component of the pulse-width-modulated signal to the output. The LC filter has an attenuation slope of -40dB/decade and introduces 180° of phase shift at frequencies above the LC resonant frequency. This phase shift in addition to the inherent 180° of phase shift of the regulator's negative feedback system turns the feedback into unstable positive feedback. The error amplifier and its associated circuitry must be designed to achieve a stable closed-loop system.

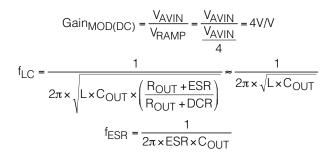

The basic controller loop consists of a power modulator (comprised of the regulator's pulse-width modulator, associated circuitry, and LC filter), an output feedback divider, and an error amplifier. The power modulator has a DC gain set by VAVIN/VRAMP where the ramp voltage (VRAMP) is a function of the VAVIN and results in a fixed DC gain of 4V/V, providing effective feed-forward compensation of input-voltage supply DC variations. The feed-forward compensation eliminates the dependency of the power modulator's gain on the input voltage such that the feedback compensation of the error amplifier requires no modifications for nominal input-voltage changes. The output filter is effectively modeled as a double-pole and a single zero set by the output inductance (L), the DC resistance of the inductor (DCR), the output capacitance (COUT) and its equivalent series resistance (ESR).

Below are equations that define the power modulator:

$R_{OUT}$  is the load resistance of the regulator,  $f_{LC}$  is the resonant break frequency of the filter, and  $f_{ESR}$  is the ESR zero of the output capacitor. See the *Closed-Loop Response and Compensation of Voltage-Mode Regulators* section for more information on  $f_{LC}$  and  $f_{ESR}$ .

The switching frequency (fsw) is programmable between 500kHz and 4MHz. Typically, the crossover frequency (fco)—the frequency at which the system's closed-loop gain is equal to unity (crosses 0dB)—should be set at or below one-tenth the switching frequency (fsw/10) for stable closed-loop response.

The MAX15021 provides an internal voltage-mode error amplifier with its inverting input and its output available to the user for external frequency compensation. The flexibility of external compensation for each controller offers a wide selection of output filtering components, especially the output capacitor. For cost-sensitive applications,

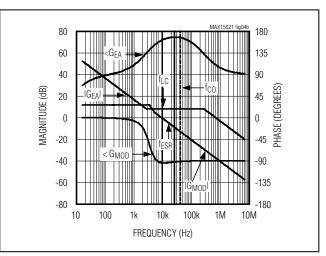

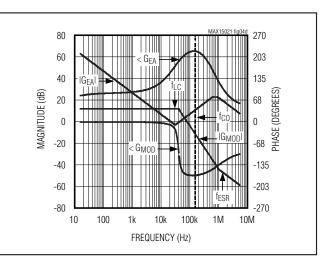

40 90 20 45 0 45 0 0 45 - 0 0 0 0 0 MAGNITUDE (dB) -20 < Смор -40 -60 -135 -80 -180 10 100 1k 10k 100k 1M 10M FREQUENCY (Hz)

Figure 4a. Power Modulator Gain and Phase Response with Lossy Bulk Output Capacitor(s) (Aluminum)

use aluminum electrolytic capacitors while for spacesensitive applications, use low-ESR tantalum or multilayer ceramic chip (MLCC) capacitors at the output. The higher switching frequencies of the MAX15021 allow the use of MLCC as the primary filter capacitor(s).

First, select the passive and active power components that meet the application output ripple, component size, and component cost requirements. Second, choose the small-signal compensation components to achieve the desired closed-loop frequency response and phase margin as outlined below.

#### Closed-Loop Response and Compensation of Voltage-Mode Regulators

The power modulator's LC lowpass filter exhibits a variety of responses, dependent on the value of the L and C and their parasitics. Higher resistive parasitics reduce the Q of the circuit, reducing the peak gain and phase of the system; however, efficiency is also reduced under these circumstances.

One such response is shown in Figure 4a. In this example, the ESR zero occurs relatively close to the filter's resonant break frequency,  $f_{LC}$ . As a result, the power modulator's uncompensated crossover is approximately one-third the desired crossover frequency,  $f_{CO}$ . Note also, the uncompensated rolloff through the 0dB plane follows a single-pole, -20dB/decade slope, and 90° of phase lag. In this instance, the inherent phase margin ensures a stable system; however, the gain-bandwidth product is not optimized.

Figure 4b. Power Modulator and Type II Compensator Gain and Phase Response with Lossy Bulk Output Capacitor(s) (Aluminum)

As seen in Figure 4b, a Type II compensator provides for stable closed-loop operation, leveraging the +20dB/ decade slope of the capacitor's ESR zero, while extending the closed-loop gain-bandwidth of the regulator. The zero crossover now occurs at approximately three times the uncompensated crossover frequency, f<sub>CO</sub>.

The Type II compensator's midfrequency gain (approximately 12dB shown here) is designed to compensate for the power modulator's attenuation at the desired crossover frequency, f<sub>CO</sub> (Gain<sub>E/A</sub> + Gain<sub>MOD</sub> = 0dB at f<sub>CO</sub>). In this example, the power modulator's inherent -20dB/decade rolloff above the ESR zero (f<sub>ZERO</sub>, ESR) is leveraged to extend the active regulation gain-bandwidth of the voltage regulator. As shown in Figure 4b, the net result is a three times increase in the regulator's gain bandwidth while providing greater than 75° of phase margin (the difference between Gain<sub>E/A</sub> and Gain<sub>MOD</sub> respective phases at crossover, f<sub>CO</sub>).

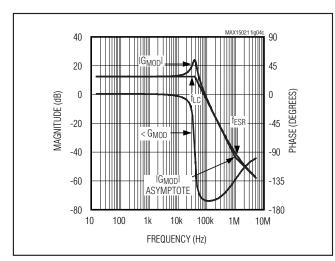

Other filter schemes pose their own problems. For instance, when choosing high-quality filter capacitor(s), e.g. MLCCs, the inherent ESR zero may occur at a much higher frequency, as shown in Figure 4c.

As with the previous example, the actual gain and phase response is overlaid on the power modulator's asymptotic gain response. One readily observes the more dramatic gain and phase transition at or near the power modulator's resonant frequency,  $f_{LC}$ , versus the

gentler response of the previous example. This is due to the filter components' lower parasitic (DCR and ESR) and corresponding higher frequency of the inherent ESR zero. In this example, the desired crossover frequency occurs below the ESR zero frequency.

In this example, a compensator with an inherent midfrequency double-zero response is required to mitigate the effects of the filter's double-pole phase lag. This is available with the Type III topology.

As demonstrated in Figure 4d, the Type III's midfrequency double-zero gain (exhibiting a +20dB/dec slope, noting the compensator's pole at the origin) is designed to compensate for the power modulator's double-pole -40dB/decade attenuation at the desired crossover frequency, f<sub>CO</sub> (again, Gain<sub>E/A</sub> + Gain<sub>MOD</sub> = 0dB at f<sub>CO</sub>) (see Figure 4d).

In the above example the power modulator's inherent (midfrequency) -40dB/decade rolloff is mitigated by the midfrequency double zero's +20dB/decade gain to extend the active regulation gain-bandwidth of the voltage regulator. As shown in Figure 4d, the net result is an approximate doubling in the controller's gain bandwidth while providing greater than 55 degrees of phase margin (the difference between Gain<sub>E/A</sub> and Gain<sub>MOD</sub> respective phases at crossover, f<sub>CO</sub>).

Design procedures for both Type II and Type III compensators are shown below.

Figure 4c. Power Modulator Gain and Phase Response with Low-Parasitic Capacitor(s) (MLCCs)

Figure 4d. Power Modulator and Type III Compensator Gain and Phase Response with Low Parasitic Capacitors (MLCCs)

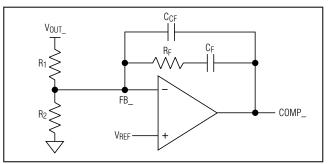

Type II: Compensation when f<sub>CO</sub> > f<sub>ZERO</sub>, ESR

When the f<sub>CO</sub> is greater than f<sub>ESR</sub>, a Type II compensation network provides the necessary closed-loop compensated response. The Type II compensation network provides a midband compensating zero and a high-frequency pole (see Figures 5a and 5b).

RFCF provides the midband zero fMID,ZERO, and RFCCF provides the high-frequency pole, fHIGH,POLE. Use the following procedure to calculate the compensation network components.

Calculate the fESR and LC double pole, fLC:

$$f_{ESR} = \frac{1}{2\pi \times ESR \times C_{OUT}}$$

$$f_{LC} \approx \frac{1}{2\pi \times \sqrt{L \times C_{OUT}}}$$

where  $C_{OUT}$  is the regulator output capacitor and ESR is the series resistance of  $C_{OUT}$ . See the *Output-Capacitor Selection* section for more information on calculating  $C_{OUT}$  and ESR.

Set the compensator's leading zero,  $f_{Z1}$ , at or below the filter's resonant double-pole frequency from:

$f_{Z1} \leq f_{LC}$

Set the compensator's high-frequency pole, fp1, at or below one-half the switching frequency, fsw:

$$f_{P1} \le \frac{f_{SW}}{2}$$

To maximize the compensator's phase lead, set the desired crossover frequency,  $f_{CO}$ , equal to the geometric mean of the compensator's leading zero,  $f_{Z1}$ , and high-frequency pole,  $f_{P1}$ , as follows:

$$f_{\rm CO} = \sqrt{f_{\rm Z1} \times f_{\rm P1}}$$

Select the feedback resistor, RF, in the range of  $3.3 \text{k}\Omega$  to  $30 \text{k}\Omega.$

Calculate the gain of the modulator ( $Gain_{MOD}$ )—comprised of the regulator's pulse-width modulator, LC filter, feedback divider, and associated circuitry—at the desired crossover frequency, f<sub>CO</sub>, using the following equation:

$$Gain_{MOD} = 4(V/V) \times \frac{ESR [m\Omega]}{(2\pi \times f_{CO}[kHz] \times L[\mu H])} \times \frac{V_{FB}[V]}{V_{OUT} [V]}$$

where  $V_{FB}$  is the 0.6V (typ) FB\_ input-voltage set-point, L is the value of the regulator inductor, ESR is the

Figure 5a. Type II Compensation Network

Figure 5b. Type II Compensation Network Response

series resistance of the output capacitor, and  $V_{\text{OUT}}$  is the desired output voltage.

The gain of the error amplifier ( $Gain_{E/A}$ ) in the midband frequencies is:

$$Gain_{E/A} = \frac{R_{F} [k\Omega]}{R_{1} [k\Omega]}$$

The total loop gain is the product of the modulator gain and the error amplifier gain at  $f_{CO}$  and should be set equal to 1 as follows:

$$Gain_{MOD} \times Gain_{E/A} = 1$$

So:

$$20 \times \log_{10} \left[ \frac{R_{F}}{R_{1}} \right] + 20 \times \log_{10} \left[ \frac{4 \times ESR \times V_{FB}}{2\pi \times f_{CO} \times L \times V_{OUT_{-}}} \right] = 0 dB$$

$$\frac{R_{F}}{R_{1}} \times \frac{4 \times ESR \times V_{FB}}{2\pi \times f_{CO} \times L \times V_{OUT}} = 1$$

MAX1502

Solving for R1:

$$R_{1} [k\Omega] = \frac{R_{F}[k\Omega] \times 4 \times \text{ESR}[m\Omega] \times V_{FB}[V]}{2\pi \times f_{CO}[kHz] \times L[\mu H] \times V_{OUT} [V]}$$

where V<sub>FB</sub> is the 0.6V (typ) FB\_ input-voltage set-point, L is the value of the regulator inductor, ESR is the series resistance of the output capacitor, and  $V_{OUT}$  is the desired output voltage.

CF is determined from the compensator's leading zero, f<sub>Z1</sub>, and RF as follows:

$$C_{\mathsf{F}}[\mu\mathsf{F}] = \frac{1}{2\pi \times \mathsf{R}_{\mathsf{F}}[k\Omega] \times \mathsf{f}_{\mathsf{Z}_{1}}[k\mathsf{H}_{\mathsf{Z}}]}$$

2) C<sub>CF</sub> is determined from the compensator's high-frequency pole, fP<sub>1</sub>, and R<sub>F</sub> as follows:

$$C_{CF}[\mu F] = \frac{1}{2\pi \times R_{F}[k\Omega] \times f_{P1}[kHz]}$$

3) Calculate R<sub>2</sub> using the following equation:

$$R_{2}[k\Omega] = R_{1}[k\Omega] \times \frac{V_{FB}[V]}{V_{OUT}[V] - V_{FB}[V]}$$

where  $V_{FB} = 0.6V$  (typ) and  $V_{OUT}$  is the output voltage of the regulator.

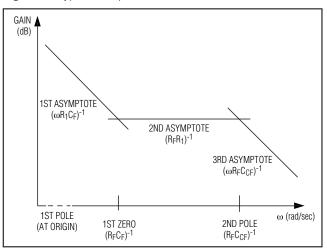

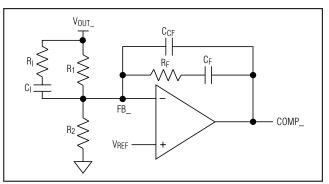

**Type III: Compensation when fco < fESR** As indicated above, the position of the output capacitor's inherent ESR zero is critical in designing an appropriate compensation network. When low-ESR ceramic output capacitors (MLCCs) are used, the ESR zero frequency (fESR) is usually much higher than the desired crossover frequency (fCO). In this case, a type III compensation network is recommended (see Figure 6a).

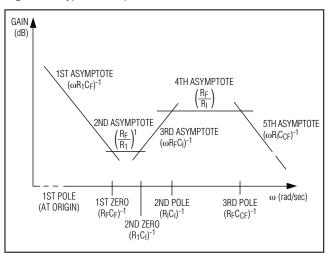

As shown in Figure 6b, the Type III compensation network introduces two zeros and three poles into the control loop. The error amplifier has a low-frequency pole at the origin, two zeros, and two higher frequency poles at the following frequencies:

$$f_{Z1} = \frac{1}{2\pi \times R_F \times C_F}$$

$$f_{Z2} = \frac{1}{2\pi \times C_I \times (R_1 + R_I)}$$

Two midband zeros ( $f_{Z1}$  and  $f_{Z2}$ ) are designed to compensate for the pair of complex poles introduced by the LC filter.

Figure 6a. Type III Compensation Network

Figure 6b. Type III Compensation Network Response

fP1 introduces a pole at zero frequency (integrator) for nulling DC output voltage errors.

f<sub>P1</sub>= at the origin (0Hz)

Depending on the location of the ESR zero (f<sub>ESR</sub>), f<sub>P2</sub> can be used to cancel it, or to provide additional attenuation of the high-frequency output ripple.

$$f_{P2} = \frac{1}{2\pi \times R_I \times C_I}$$

fp3 attenuates the high-frequency output ripple.

$$f_{P3} = \frac{1}{2\pi \times R_F \times (C_F \| C_{CF})} = \frac{1}{2\pi \times R_F \times \frac{C_F \times C_{CF}}{C_F + C_{CF}}}$$

Since C<sub>CF</sub> << C<sub>F</sub> then:

$$f_{P3} = \frac{1}{2\pi \times R_F \times C_{CF}}$$

# MAX15021

## Dual, 4A/2A, 4MHz, Step-Down DC-DC Regulator with Tracking/Sequencing Capability

The locations of the zeros and poles should be such that the phase margin peaks around f<sub>CO</sub>.

Set the ratios of f<sub>CO</sub>-to-f<sub>Z</sub> and f<sub>P</sub>-to-f<sub>CO</sub> equal to one another, e.g.,  $\frac{f_{CO}}{f_Z} = \frac{f_P}{f_{CO}} = 5$  is a good number to get approximately

$60^\circ$  of phase margin at  $f_{CO}.$  Whichever technique, it is important to place the two zeros at or below the double pole to avoid the conditional stability issue.

The following procedure is recommended:

1) Select a crossover frequency, f<sub>CO</sub>, at or below onetenth the switching frequency (f<sub>SW</sub>):

$$f_{CO}[kHz] \le \frac{f_{SW}[kHz]}{10}$$

2) Calculate the LC double-pole frequency, fLC :

$$f_{LC}[MHz] \approx \frac{1}{2\pi \times \sqrt{L[\mu H] \times C_{OUT}[\mu F]}}$$

where  $C_{OUT}$  is the output capacitor of the regulator.

- 3) Select the feedback resistor, R<sub>F</sub>, in the range of  $3.3k\Omega$  to  $30k\Omega$ .

- 4) Place the compensator's first  $f_{Z1} = \frac{1}{2\pi \times R_F \times C_F}$ zero at or below the output filter's double-pole, f<sub>LC</sub>, as follows:

$$C_{F}[\mu F] = \frac{I}{2\pi \times R_{F}[k\Omega] \times 0.5 \times f_{LC}[kHz]}$$

5) The gain of the modulator (Gain<sub>MOD</sub>)—comprised of the regulator's pulse-width modulator, LC filter, feedback divider, and associated circuitry—at the crossover frequency is:

$$Gain_{MOD} = 4 \times \frac{1}{(2\pi \times f_{CO}[MHz])^2 \times L[\mu H] \times C_{OUT}[\mu F]}$$

The gain of the error amplifier (Gain $\ensuremath{\mathsf{E/A}}\xspace)$  in midband frequencies is:

$$Gain_{E/A} = 2\pi \times f_{CO}[kHz] \times C_{I}[\mu F] \times R_{F}[k\Omega]$$

The total loop gain is the product of the modulator gain and the error amplifier gain at  $f_{\rm CO}$  should be equal to 1, as follows:

$Gain_{MOD} \times Gain_{E/A} = 1$

So:

$\begin{array}{l} 4 \times \frac{1}{\left(2\pi \times f_{\text{CO}}[\text{kHz}]\right)^2 \times C_{\text{OUT}}[\mu\text{F}] \times L[\mu\text{H}]} \\ \times 2\pi \times f_{\text{CO}}[\text{kHz}] \times C_{\text{I}}[\text{pF}] \times \text{R}_{\text{F}}[\text{k}\Omega] = 1 \end{array}$

MAXIM .

Solving for CI:

$$C_{I}[pF] = \frac{(2\pi \times f_{CO}[kHz] \times L[\mu H] \times C_{OUT}[\mu F])}{4 \times R_{F}[k\Omega]}$$

6) For those situations where f<sub>LC</sub> < f<sub>CO</sub> < f<sub>ESR</sub> < f<sub>SW</sub>/2, as with low-ESR tantalum capacitors, the compensator's second pole (f<sub>P2</sub>) should be used to cancel f<sub>ESR</sub>. This provides additional phase margin. On the system Bode plot, the loop gain maintains its +20dB/decade slope up to <sup>1</sup>/<sub>2</sub> of the switching frequency verses flattening out soon after the 0dB crossover. Then set:

If a ceramic capacitor is used, then the capacitor ESR zero, f<sub>ESR</sub>, is likely to be located even above one-half of the switching frequency, that is  $f_{LC} < f_{CO} < f_{SW}/2 < f_{ESR}$ . In this case, the frequency of the second pole (f<sub>P2</sub>) should be placed high enough not to significantly erode the phase margin at the crossover frequency. For example, f<sub>P2</sub> can be set at 5 x f<sub>CO</sub>, so that its contribution to phase loss at the crossover frequency f<sub>CO</sub> is only about 11°:

$$f_{P2} = 5 \times f_{CO}$$

Once fP2 is known, calculate RI:

$$\mathsf{R}_{\mathsf{I}}[\mathsf{k}\Omega] = \frac{1}{2\pi \times \mathsf{f}_{\mathsf{P2}}[\mathsf{k}\mathsf{Hz}] \times \mathsf{C}_{\mathsf{I}}[\mu\mathsf{F}]}$$

Place the second zero (fz<sub>2</sub>) at 0.2 x f<sub>CO</sub> or at f<sub>LC</sub>, whichever is lower, and calculate R<sub>1</sub> using the following equation:

$$R_{1}[k\Omega] = \frac{1}{2\pi \times f_{Z2}[kHz] \times C_{I}[\mu F]}$$

8) Place the third pole (fp<sub>3</sub>) at 1/2 the switching frequency and calculate C<sub>CF</sub> from:

$$C_{CF}[nF] = \frac{1}{\left(2\pi \times 0.5 \times f_{SW}[MHz] \times R_{F}[k\Omega]\right)}$$

9) Calculate R<sub>2</sub> as:

$$R_{2}[k\Omega] = R_{1}[k\Omega] \times \frac{V_{FB}[V]}{V_{OUT}[V] - V_{FB}[V]}$$

where  $V_{FB} = 0.6V$  (typ).

## **Applications Information**

#### **PCB** Layout Guidelines

Careful PCB layout is critical to achieve clean and stable operation. Follow these guidelines for good PCB layout:

- 1) Place decoupling capacitors as close as possible to the IC pins.

- 2) Keep SGND and PGND isolated and connect them at one single point close to the negative terminal of the input filter capacitor.

- 3) Route high-speed switching nodes away from sensitive analog areas (FB\_, COMP\_, and EN\_).

- 4) Distribute the power components evenly across the board for proper heat dissipation.

- 5) Ensure timing resistor and all feedback connections are short and direct. Place feedback resistors as close as possible to the IC.

- 6) Place the bank of the output capacitors close to the load.

- 7) Connect the MAX15021 exposed pad to a large copper plane to maximize its power dissipation capability. Connect the exposed pad to SGND plane. Do not connect the exposed pad to the SGND pin directly underneath the IC.

- Use 2oz. copper to keep trace inductance and resistance to a minimum. Thin copper PCBs can compromise efficiency since high currents are involved in the application. Also thicker copper conducts heat more effectively, thereby reducing thermal impedance.

- 9) A reference PCB layout included in the MAX15021 Evaluation Kit is also provided to further aid layout.

MAX15021

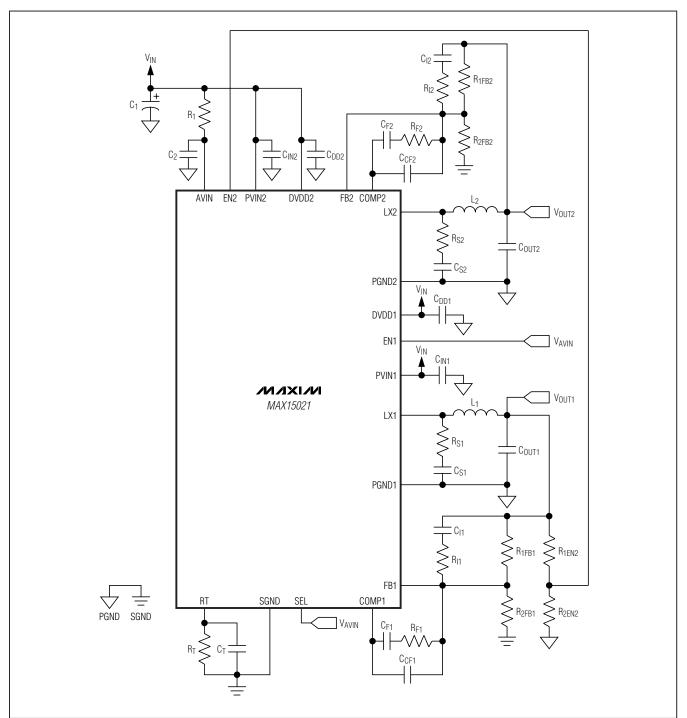

## **Typical Operating Circuits**

MAX15021

Figure 7. MAX15021 Double Buck with Tracking

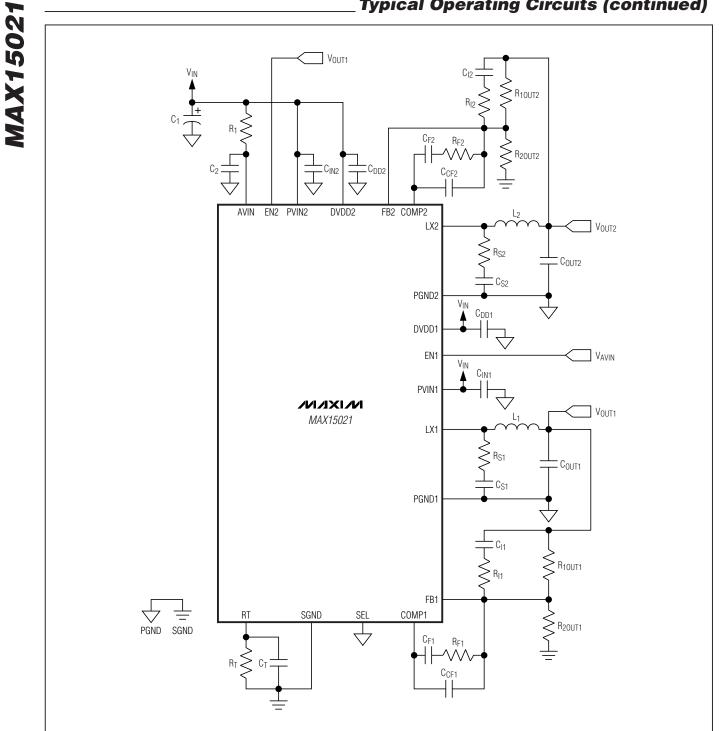

**Typical Operating Circuits (continued)**

Figure 8. MAX15021 Double Buck with Sequencing

## **Chip Information**

PROCESS: BICMOS

## **Package Information**

For the latest package outline information, go to **www.maxim-ic.com/packages**.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 28 TQFN      | T2855-6      | <u>21-0140</u> |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

**MAXIM** is a registered trademark of Maxim Integrated Products, Inc.

\_\_\_ 23